PROBLEMA: Dados los siguientes diagramas de tiempo para el flip-flop J-K, obténganse los diagramas de tiempo a la salida del mismo en las terminales Q y Q a partir de los diagramas de tiempo proporcionados. Supóngase que el flip-flop J-K está inicialmente en el estado Q=0. Supóngase también que los cambios son motivados por las transiciones de "1" a "0" en la terminal C y que en el estado J=1 y K=1 la terminal C no ejerce ninguna acción.

La salida en la terminal Q basada en las características del flip-flop J-K suponiendo que inicialmente Q=0 es como se muestra a continuación:

La explicación del diagrama de tiempos de la salida Q es la siguiente:

Suponiendo que el flip-flop J-K está inicialmente en el estado Q=0, la transición de "0" a "1" en la terminal C no produce efecto alguno, pero la caída subsecuente de "1" a "0" hace que el flip-flop J-K cambie de estado, pasando de Q=0 a Q=1. La siguiente transición negativa de "1" a "0" en la terminal C hace que la salida Q vuelva a cambiar de estado, pasando de Q=1 a Q=0. Tras esto, aparecen unos "pulsos" en las terminales J y K, pero estos no tienen efecto alguno al permanecer la terminal C en un nivel estático. Tras ascender nuevamente la terminal C de "0" a "1", hay un cambio en el valor de entrada en la terminal J, que es puesta a J=1. Esto prepara al flip-flop para que cuando haya una transición negativa de "1" a "0" en la terminal C el flip-flop J-K pase al estado Q=1 al tener J=1 y K=0 en sus terminales de entrada, que es precisamente lo que ocurre al final del tercer "pulso" en la terminal C. Tras esto, después de que la entrada en la terminal J cae de "1" a "0" sin producir cambio alguno puesto que los cambios los produce únicamente la terminal C, la terminal C sube de "0" a "1" sin producir todavía cambio alguno en la salida, y permanece en "1" mientras el valor en la terminal K sube de "0" a "1". Esto prepara al flip-flop para que cuando haya una transición negativa de "1" a "0" en la terminal C el flip-flop J-K pase al estado Q=0 al tener J=0 y K=1 en sus terminales de entrada, que es precisamente lo que ocurre al final del cuarto "pulso" en la terminal C. Tras esto, la entrada J es elevada de "0" a "1", con lo cual ambas entradas J y K tienen el valor de "1", lo cual tiene como consecuencia directa que cuando ocurran los siguientes dos "pulsos" en la señal de "reloj" C el flip-flop J-K no cambie de estado.

Puesto que la salida en la terminal Q es simplemente el complemento (inverso lógico) de la salida en la terminal Q, el aspecto del diagrama de tiempos mostrado por esta terminal será el siguiente:

PROBLEMA: Demostrar que la salida de un flip-flop J-K, después de que ha ocurrido una transición, está dada por:

Qn+1 = JQn + K·Qn

en donde Qn es la salida del flip-flop J-K antes de llevarse a cabo la transición.

Tomando en cuenta las propiedades del flip-flop J-K, se puede desarrollar la siguiente Tabla de Verdad:

De la Tabla de Verdad se puede obtener ahora Qn+1 en función de J, K y Qn por medio de minterms:

Qn+1 = J·K·Qn + J·K·Qn + J·K·Qn + JKQn

Qn+1 = (J + J)·K·Qn + (K + K)JQn

Qn+1 = JQn + K·Qn

Para facilitar la comprensión del diseño, se reproducen primero el diagrama esquemático y la Tabla de Verdad del flip-flop R-S hecho con bloques NOR:

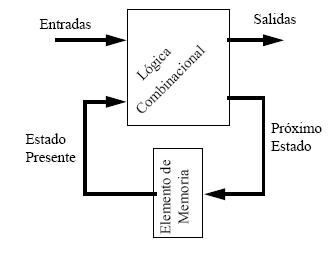

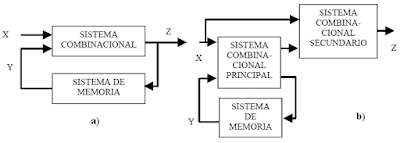

Es necesario diseñar primero una configuración en la cual la información a la entrada sea transferida a la salida únicamente cuando la terminal de "reloj" C vaya del estado "1" al estado "0", justo cuando ocurre la transición. Esto presupone necesariamente dos pasos, a saber:

(A) Cuando la terminal C va de "0" a "1".- La configuración es "preparada" para el cambio que habrá de ocurrir. Se almacena dentro de la configuración interna del elemento la información que está puesta a la entrada del mismo.

(B) Cuando la terminal C va de "1" a "0".- La salida de la configuración adquiere el estado a su entrada que fue almacenado por la misma durante la transición de "0" a "1". Esto sugiere el uso de dos flip-flops R-S para construír la configuración.

Para poder implementar lo anterior, se requiere un circuito con dos flip-flops R-S en una configuración maestro-esclavo (master-slave) como se muestra a continuación:

El tipo de compuerta usado debe permitir el flujo de información al ser activada con un "1" y detener todo flujo de información al ser desactivada con un "0". Al ser desactivada con un "0", su salida en sus dos terminales debe ser "0" para que el flip-flop R-S que le sigue retenga al información que se deseaba almacenar (o sea, viendo la Tabla de Verdad del flip-flop R-S hecho con bloques NOR, se requiere que R=0 y S=0 para que el flip-flop retena su estado anterior). Este tipo de compuerta ya lo hemos visto previamente. Se puede construír fácilmente usando funciones AND como se muestra a continuación:

Al ir la terminal C de "0" a "1", la compuerta de entrada permite que se almacene en el flip-flop maestro la información a la entrada de la configuración, a la vez que la compuerta de transferencia entre los dos flip-flops impide que esta información altere la información que está puesta a la salida de la configuración, porque se requiere que la salida permanezca inalterada en la transición positiva de la señal de "reloj".

Al ir la terminal C de "1" a "0", la compuerta de transferencia permite que el flip-flop maestro "imponga" su estado en el flip-flop esclavo, a la vez que la compuerta de entrada detiene todo nuevo flujo de información a la entrada de la configuración, conservando así el flip-flop maestro su estado que está siendo transmitido al flip-flop esclavo.

En el siguiente gráfico animado (ampliar imagen para poder ver la animación en acción) se muestra una configuración "maestro-esclavo" de flip-flops hechos con bloques NAND:

En el extremo superior izquierdo tenemos la simulación de un osciloscopio actuando como analizador lógico que nos permite ver el pulso que está siendo aplicado en la terminal de "reloj" C a la entrada del circuito. Obsérvense las dos acciones que ocurren cuando (a) el pulso de entrada va de "0" a "1", y (b) cuando va de "1" a "0".

Falta ahora relacionar las entradas S0 y R0 del circuito con las terminales J y K externas al circuito que le vamos a agregar y que eventualmente identificaremos como las terminales J y K, tomando en cuenta el estado en el cual se encuentra la salida Q del segundo flip-flop (el flip-flop esclavo) que vendría siendo la salida de todo el circuito.

Cuando J=1 y K=0, si Q=0 entonces después de una transición el circuito quedará en el estado Q=1. Para que esto ocurra en nuestra configuración se requiere que S0=1 y R0=0. Representando esto en una Tabla de Verdad:

Cuando J=1 y K=0, si Q=1 entonces el flip-flop J-K conservará su estado sin que lo afecten las transiciones en la terminal C. En nuestra configuración esto equivale a tener S0=0 y R0=0 para que retenga su estado y sea inmune a las transiciones en la terminal C. Por lo tanto:

Usando razonamientos como los anteriores, encontramos también que:

Cuando J=1 y K=1, el flip-flop J-K retiene su estado anterior (ya sea Q=1 ó Q=0) sin que lo afecten las transiciones en la terminal C. Para lograr el mismo efecto, nuestra configuración requiere S0=0 y R0=0. Por lo tanto:

Cuando J=0 y K=0, el flip-flop J-K cambia de estado después de cada transición. Si J=0, K=0 y Q=0, el flip-flop J-K cambiará al estado Q=1 después de una transición, efecto que obtenemos en nuestro circuito con S0=1 y R0=0. Por lo tanto:

Asimismo, cuando J=0, K=0 y Q=1, el flip-flop J-K cambiará al estado Q=0 después de una transición, lo cual se logra en nuestro circuito con con S0=0 y R0=1. Por lo tanto:

Juntando toda la información anterior en una sola Tabla de Verdad:

Podemos ahora obtener los valores Boleanos que deben tener S0 y R0 en función de los valores que tengan J y K para que nuestra configuración se pueda comportar como un flip-flop J-K. Usando minterms:

S0 = J·K·Q + J·K·Q

S0 = (J + J)K·Q

S0 = K·Q

S0 = K + Q

y:

R0 = J·K·Q + JKQ

R0 = JQ(K + K)

R0 = JQ

En esta última línea podemos aplicar "a la inversa" una de las leyes de DeMorgan de la siguiente manera:

para obtener así una expresión final para R0 que se pueda construír mediante un bloque NOR.

Con estas dos relaciones para S0 y R0 implementables con bloques NOR (éste fue a fin de cuentas el objetivo verdadero detrás de las manipulaciones Boleanas mostradas), las cuales llevan a cabo primero la suma Boleana de las entradas y tras esto efectúan el complemento de la suma, podemos ver que el diseño del circuito toma ahora el siguiente aspecto:

PROBLEMA: Con la ayuda de un analizador lógico, un técnico obtiene en la carátula del analizador los siguientes diagramas de tiempo para un flip-flop J-K:

¿Qué tipo de flip-flop J-K es el que describen estos diagramas de tiempo?

Explicar en detalle lo que está sucediendo desde el principio hasta el final de los diagramas de tiempo.

Comparando los pulsos de entrada en la terminal de reloj C (clock) con lo que ocurre a la salida Q del flip-flop, es obvio que las transiciones ocurren para este flip-flop cuando la señal de reloj va de "0" a "1" en vez de ocurrir cuando va de "1" a "0". Este flip-flop J-K es por lo tanto uno activado por las transiciones positivas (de "0" a "1") en la terminal de "reloj".

Al principio, la terminal J sube de "0" a "1". Pero como no es esta terminal la que produce las transiciones, no ocurre nada. Tras esto, la señal de "reloj" sube de "0" a "1", y por estar las entradas del flip-flop J-K puestas a J=1 y K=o cuando esto ocurre, el flip-flop que estaba en el estado Q=0 pasa al estado Q=1, mientras que su salida complementaria que estaba en el estado Q=1 pasa al estado Q=0. Una vez que esto ha ocurrido, la entrada J es bajada de "1" a "0" y tras esto la entrada K es subida de "0" a "1", de modo tal que cuando la señal de "reloj" sube de "0" a "1" estando puestas las entradas a J=0 y K=1 en el siguiente ascenso positivo del pulso posterior del "reloj" el estado Q=1 pasa a ser el estado Q=0, mientras que la salida complementaria que estaba en el estado Q=0 pasa al estado Q=1. Posteriormente la señal en la entrada K cae de "1" a "0" y vuelve a subir de "0" a "1", lo cual por sí solo no tiene efecto alguno en el comportamiento del flip-flop, y al ocurrir la tercera transición positiva del pulso de reloj las entradas están a los mismos valores J=0 y K=1 que tenían en la transición anterior, de manera que no se manifiesta cambio alguno. Entre el tercer y el cuarto pulso de reloj hay transiciones en las terminales J y K que no producen cambio alguno, como era de esperarse. En la cuarta transición positiva de la señal de reloj las terminales J y K están ambas al mismo valor de "1", y se produce una transición de Q=1 a Q=0, repitiéndose los cambios que hacen que el flip-flip J-K transite entre estados opuestos con cada transición positiva de la señal de reloj. Esto nos confirma que el flip-flop J-K está construído con bloques NAND.

PROBLEMA: Ilustrar una manera en la cual se pueda poner de modo "forzado" al flip-flop J-K ya sea en el estado Q=0 o en el estado Q=1 sin necesidad de tener que utilizar una terminal C.

Tomando como base el diseño previo de un flip-flop J-K construído con bloques NOR, esto se puede lograr usando flip-flops de tres entradas en lugar de dos en el flip-flop esclavo de la configuración. Dicho elemento tomará el siguiente aspecto:

Estudiando la configuración y tomando en cuenta las propiedades del flip-flop J-K hecho con bloques NOR, encontramos que al activar la terminal Rd de acción "directa" hacia la salida Q con un "1", el flip-flop J-K es forzado a entrar en la condición Q=0. Asimismo, al activar la terminal Sdcon un "1" el flip-flop J-K es forzado a entrar en la condición Q=1. Se puede observar que ambas terminales Rd y Sd no deben ser activadas al mismo tiempo, ya que se colocaría al flip-flop esclavo interno (y por lo tanto al flip-flop J-K en un estado no-definido. También podemos observar que mientras una de las terminales permanezca activada, el flip-flop J-K no responderá a los valores que tomen las entradas J, K y C.

Una forma de representar un flip-flop J-K con terminales de "limpieza" R y "preajuste" S directas es como sigue:

Nótese que la cercanía de la terminal S con la salida Q sugiere que al ser activada S el "1" con el cual es activada pasa a la salida más cercana que es en este caso Q. De la misma manera, al ser activada R, el "1" con el cual es activada pasa a Q.

En la literatura técnica es frecuente llamar a las terminales R y S como "clear" y "preclear". Desafortunadamente, al abreviar el símbolo de la terminal de "limpieza" clear con la letra C (de clear) se puede confundir con el símbolo para la terminal de reloj C que para evitar confusiones a veces es redesignada como CLK.

Los circuitos integrados comerciales flip-flops J-K puestos a la venta generalmente tienen incluídas estas terminales de "limpieza", y como ejemplo de ello se puede citar el circuito integrado 4027fabricado con tecnología CMOS:

el cual incluye dos flip-flops J-K (simbolizados en el diagrama como F/F). En el flip-flop 1, el equivalente de nuestra terminal S que forza al flip-flop a entrar en el estado Q=1 está puesto en la terminal 9 del circuito integrado (SET 1), mientras que el equivalente de nuestra terminal R que "limpia" al flip-flop poniéndolo en el estado Q=0 está puesto en la terminal 12 del circuito integrado (RESET 1).

El uso de terminales de "limpieza" en cada circuito de memoria es sumamente útil cuando se enciende un sistema digital que había estado apagado por algún tiempo, ya que durante el proceso de encendido cada uno de los elementos de memoria puede entrar en un estado de "1" ó en un estado de "0" de manera completamente aleatoria, lo cual podría ser reinterpretado erróneamente por el sistema al empezar a funcionar. La "limpieza" de todos los registros de memoria garantiza de que no habrá nada en los registros que pueda ser malinterpretado durante el procedimiento de arranque. Este proceso de "limpieza" es precisamente lo que se lleva a cabo cada vez que se enciende una computadora de escritorio o que se oprime el botón de RESET (en las que lo tienen) para volver a comenzar de nuevo desde cero, literalmente, en todos los registros de memoria.